## **Objectives**

After completing this module, you will be able to...

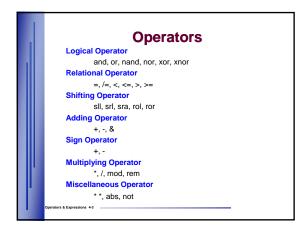

- · Write standard VHDL expressions

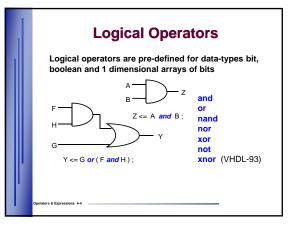

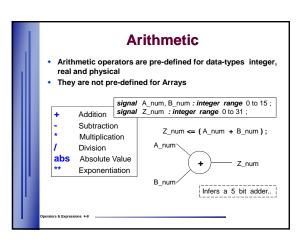

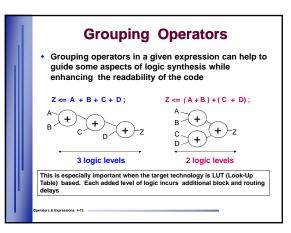

- Infer logic and functionality using VHDL operators

- Apply appropriate operators to each data-type

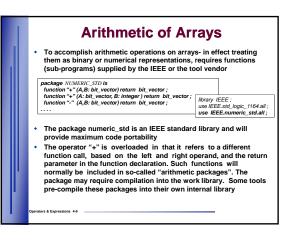

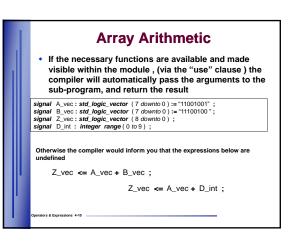

- Reference appropriate packages for arithmetic functions

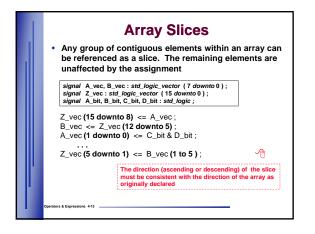

- Use VHDL 'slice' to reference sub-bus structures

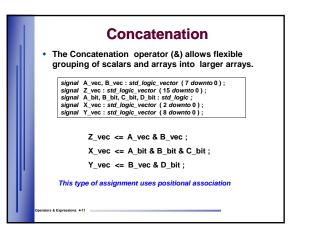

- Use VHDL 'concatenation' operator

## Answers

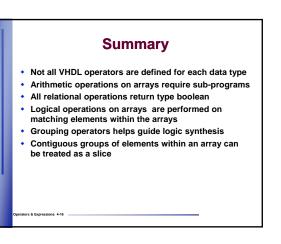

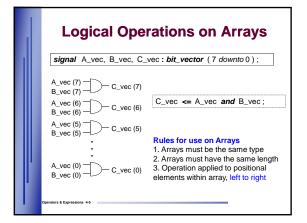

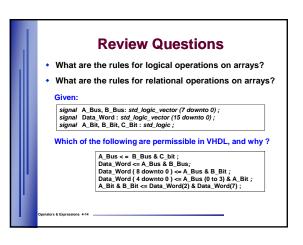

What are the rules for logical operations on arrays?

—Size & type must match, operation applied to matching

elements (left to right)

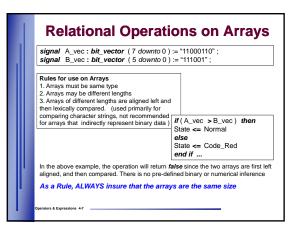

What are the rules for relational operations on arrays?

Type must match, if size is different, arrays are left aligned then lexically compared

Which of the following are permissible in VHDL, and why  $\ensuremath{\mathsf{?}}$

A\_Bus <= B\_Bus & C\_bit; BAD, size mismatch, type OK Data\_Word <= A\_Bus & B\_Bus; OK, size and type match Data\_Word ( & downto 0) <= A\_Bus & B\_Bit; OK, size and type match Data\_Word ( & downto 0) <= A\_Bus (0 to 3) & A\_Bit; BAD, null sidec on 'A\_Bus' A\_Bit & B\_Bit <= Data\_Word(2) & Data\_Word(7); OK, size and type match

& Expressions 4-15