## **Objectives** After completing this module, you will be able to... • Declare ports and signals using appropriate data-types • Define all possible values for each data-types • Declare 'array' for composite data-types • Assign to 'array' or 'scalar' object • Create and use 'enumerated' data-types

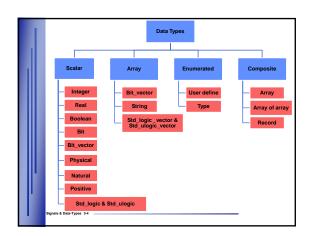

## **Data-Types**

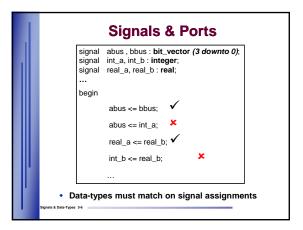

- Data-types are very important in VHDL. A given datatype allows only values within its range to be applied. Each object (signal, variable, constant) or port must have its type defined when declared

- VHDL is considered to be a strongly typed language. Connected signals must be of the same type

- The wide range of data-types available provides both flexibility in hardware modeling and built-in error checking to ensure signal compatibility in large and complex models. This checking exists for behavioral simulation, not RTL/gate level implementation

Data-Types 3-3

|      |                          | Standard Data Types<br>n package STANDARD            |

|------|--------------------------|------------------------------------------------------|

| di - | Туре                     | Range of Values                                      |

|      | Integer                  | -2,147,483,647 to +2,147,483,647                     |

|      | Real                     | -1.0E+38 to +1.0E+38                                 |

|      | Boolean                  | (TRUE, FALSE)                                        |

|      | Character                | Defined in package STANDARD                          |

|      | Bit                      | '0' , '1'                                            |

|      | Bit_vector               | Array with each element of type bit                  |

|      | Time                     | Fs, ps, ns, us, ms, sec, min, hr                     |

|      | String                   | Array with each element of type character            |

|      | Natural                  | 0 to the maximum integer value in the implementation |

|      | Positive                 | 1 to the maximum integer value in the implementation |

|      | Signals & Data-Types 3-5 |                                                      |

|                                                                  | architecture BEHAVE of MUX is<br>signal A,B,Sel, Z : bit ;<br>begin<br>if Sel = '1' then               |

|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| type <b>bit</b> is ( <b>'0', '1'</b> ) ;                         | If Sel = 1 then<br>Z <= A;<br>else<br>Z <= B;<br>end if                                                |

| Type bit is helpful and concise<br>not provide for high-impedanc | 5                                                                                                      |

| type <b>boolean</b> is ( false, tr                               | $\begin{array}{c} \text{if Sel ='1',  if  F \ >= \ G} \\ \text{both yield boolean result} \end{array}$ |

| ALC: 1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.                      |                                                                                                        |

|      | signal<br>signal<br>signal<br>signal | abus : std_ulogic_vec<br>res_z: std_logic; |              |             |  |

|------|--------------------------------------|--------------------------------------------|--------------|-------------|--|

|      | <br>begin                            |                                            |              |             |  |

|      |                                      | z <= a;                                    | $\checkmark$ | res_z <= a; |  |

|      |                                      | res_z <= a;                                | $\checkmark$ | res_z <= b; |  |

|      |                                      | a<= res_z;                                 | ×            |             |  |

|      |                                      | res_zbus <= abus;                          | $\checkmark$ | z <= a;     |  |

| ľ. – |                                      | abus <= res zbus;                          | ×            | z <= b;     |  |

|   | Recor                                                                                                                                                                                                                     | ds                                                                           |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

|   | type OPCODE is record<br>PARITY : bit;<br>ADDRESS : std_logic_vector (0 to 3);<br>DATA_BYTE : std_logic_vector (7 downto 0);<br>NUM_VALUE : integer range 0 to 6;<br>STOP_BITS : bit_vector (1 downto 0);<br>end record ; | 0 );<br>Records are groups of<br>elements, that may be of<br>different types |

|   | signal TX_PACKET, RX_PACKET : OPCO                                                                                                                                                                                        | DE;                                                                          |

|   | PARITY ← ADDRESS → ← DATA_BYT                                                                                                                                                                                             | re → ← num_value stop_bits                                                   |

|   | TX_PAC                                                                                                                                                                                                                    | КЕТ                                                                          |

| ľ | Signals & Data-Types 3-19                                                                                                                                                                                                 |                                                                              |

| Answers                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------|

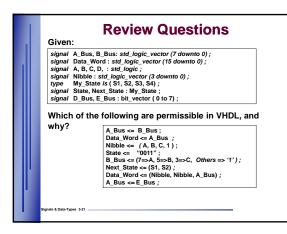

| Given:                                                                                                                    |

| signal A_Bus, B_Bus: std_logic_vector (7 downto 0) ;                                                                      |

| signal Data_Word : std_logic_vector (15 downto 0) ;                                                                       |

| signal A, B, C, D, : std_logic ;                                                                                          |

| signal Nibble : std_logic_vector (3 downto 0) ;                                                                           |

| type My_State is (S1, S2, S3, S4);                                                                                        |

| signal State, Next_State : My_State ;<br>signal D Bus, E Bus : bit_vector ( 0 to 7) ;                                     |

| signal D_bus, E_bus : bit_vector (0 to 7);                                                                                |

| Which of the following are permissible in VHDL, and                                                                       |

| why?                                                                                                                      |

| why?<br>A_Bus <= B_Bus ; OK, size and type are the same                                                                   |

| why?                                                                                                                      |

| why?<br>A_Bus <= B_Bus ; OK, size and type are the same<br>Data_Word <= A_Bus ; BAD, size mismatch, although type matches |

| why?   OK, size and type are the same     Data_Word <= A_Bus;                                                             |

| why?   A_Bus <= B_Bus;                                                                                                    |

| why?   OK, size and type are the same     Data_Word <= A_Bus;                                                             |

## Summary

- Each object and port must have its type defined

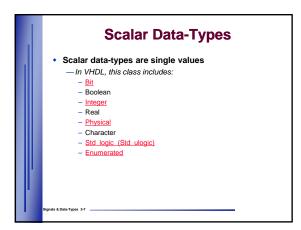

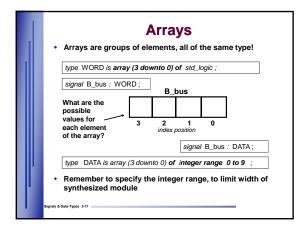

- VHDL provides scalar and composite data-types

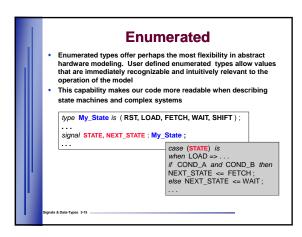

- Enumerated types can be used to enhance code readability

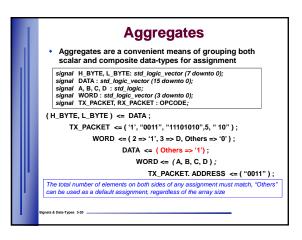

- Aggregates assignments can be made for arrays and records

- Types on connecting signals must match

s & Data-Types 3-23